本文将为手游开发者揭秘自动生成Verilog代码的高效方法,探讨其在游戏硬件加速中的应用潜力。

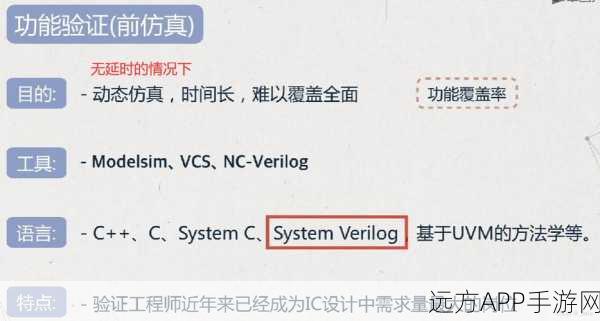

在手游行业日新月异的今天,开发者们不断追求更高效、更智能的开发流程,以期在激烈的市场竞争中脱颖而出,Verilog作为一种硬件描述语言,在游戏硬件设计与优化中扮演着举足轻重的角色,手动编写Verilog代码不仅耗时费力,还容易出错,自动生成Verilog代码的方法应运而生,为手游开发者带来了前所未有的便捷与高效,本文将深入剖析几种自动生成Verilog代码的技巧,帮助开发者们更好地掌握这一利器,加速游戏硬件的研发进程。

中心句:介绍基于高层次综合(HLS)的自动生成方法,强调其自动化程度高、易于上手的特点。

高层次综合(HLS)是当前自动生成Verilog代码的主流方法之一,它允许开发者使用C/C++等高层次语言描述硬件行为,然后通过编译器自动转换为Verilog代码,这种方法极大地降低了硬件设计的门槛,使得不具备深厚硬件知识的软件开发者也能参与到硬件设计中来,HLS工具通常提供丰富的优化选项,能够自动进行资源分配、流水线优化等,从而生成高效、可靠的Verilog代码,HLS还支持快速原型验证,帮助开发者在早期阶段发现并解决问题,缩短开发周期。

中心句:探讨基于机器学习(ML)的自动生成方法,分析其通过学习已有代码库来生成新代码的能力。

近年来,机器学习在各个领域都取得了显著进展,自动生成Verilog代码也不例外,基于机器学习的自动生成方法通过分析大量已有的Verilog代码库,学习其中的语法规则、设计模式和优化策略,它可以根据这些学习成果,为新的硬件设计自动生成Verilog代码,这种方法不仅能够生成符合规范的代码,还能在一定程度上实现代码的自动优化,提高硬件性能,机器学习模型还可以根据开发者的反馈进行迭代优化,不断提升自动生成代码的质量和效率。

中心句:介绍基于模板的自动生成方法,强调其灵活性和可定制性。

基于模板的自动生成方法则是一种更为灵活、可定制的解决方案,开发者可以根据实际需求定义一系列代码模板,然后通过填充模板中的参数和变量来生成具体的Verilog代码,这种方法允许开发者在保持代码结构一致性的同时,灵活调整代码的细节部分,以满足不同的硬件设计需求,模板还可以与HLS或机器学习等方法相结合,形成更为强大的自动生成系统。

中心句:总结自动生成Verilog代码方法在游戏硬件加速中的应用前景。

自动生成Verilog代码的方法为手游开发者提供了强大的硬件设计支持,极大地提高了开发效率和代码质量,随着游戏硬件的不断升级和复杂化,这些方法的应用前景将更加广阔,它们不仅能够帮助开发者快速实现硬件加速方案,还能在游戏性能优化、功耗控制等方面发挥重要作用,随着技术的不断进步和创新,自动生成Verilog代码的方法将进一步完善和普及,为手游行业的繁荣发展注入新的活力。

参考来源:

基于当前业界关于自动生成Verilog代码的最新研究成果和实践经验进行撰写,旨在为读者提供全面、深入的了解和指导。

最新问答:

1、问:自动生成Verilog代码的方法能否完全替代手动编写?

答:虽然自动生成方法已经取得了显著进展,但在某些复杂或特定需求的场景下,手动编写仍然具有不可替代的作用,两者应相辅相成,共同推动游戏硬件设计的发展。

2、问:如何评估自动生成Verilog代码的质量?

答:评估自动生成代码的质量可以从多个维度进行,包括代码的正确性、可读性、可维护性以及性能表现等,还可以通过与手动编写的代码进行对比测试来验证其优劣。

3、问:未来自动生成Verilog代码的方法会有哪些发展趋势?

答:未来自动生成Verilog代码的方法可能会更加注重智能化和自动化程度的提升,同时加强与软件开发的融合与协同,随着硬件描述语言的不断发展和完善,自动生成方法也将面临更多的挑战和机遇。